introduction

There are many methods to solve EMI problems, and modern EMI suppression techniques include using EMI suppression coatings, selecting appropriate EMI suppression components, and performing EMI simulation design. This article discusses the role of PCB layering and stacking in controlling EMI radiation, along with design tips.

Electromagnetic Shielding

From the perspective of signal routing, an effective layering strategy should place all signal traces on one or several layers, closely adjacent to the power or ground layers. For power layers, an effective strategy is to have the power layer next to the ground layer, minimizing the distance between them. This is what we refer to as a "layering" strategy.

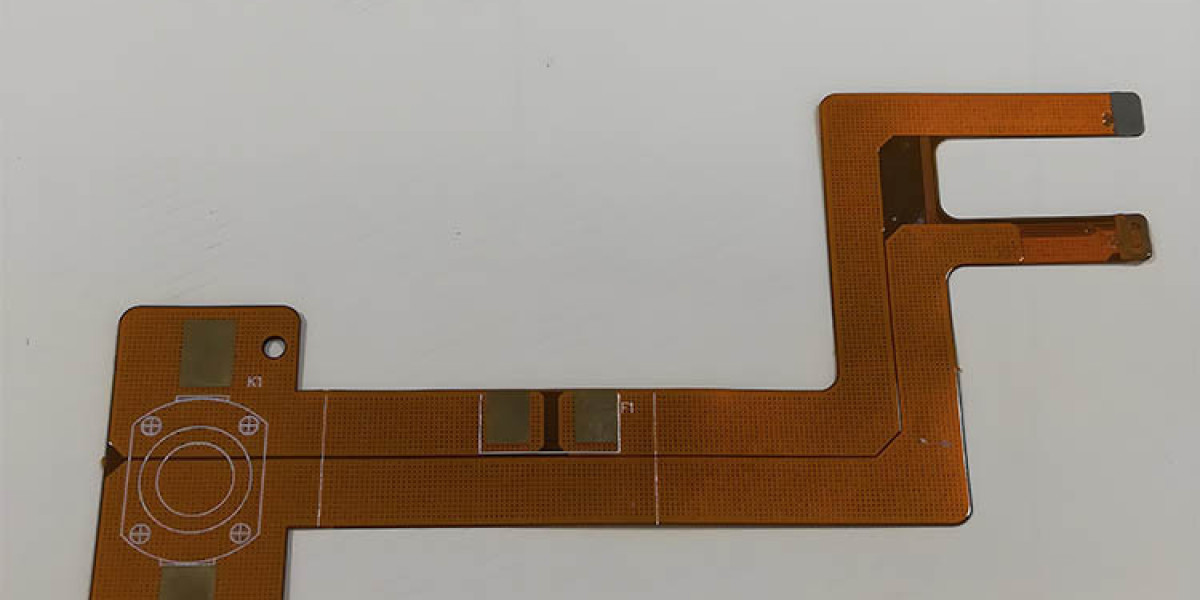

PCB Stacking

What kind of stacking strategy helps with shielding and suppressing EMI? The following layering schemes assume that power currents flow on a single layer, with single or multiple voltages distributed across different sections of the same layer. The situation with multiple power layers will be discussed later.

4-Layer Boards

Designing a 4-layer board presents several potential issues. First, for traditional 62-mill thick four-layer boards, even with the signal layer on the outer layer and the power and ground layers on the inner layers, the distance between the power and ground layers remains too large.

If cost is the primary concern, consider two traditional 4-layer board alternatives. Both options can improve EMI suppression performance, but they are only suitable when the component density on the board is sufficiently low and there is enough area around the components to place the required power copper pour.

The first option is preferred: the outer layers of the PCB are both ground layers, while the middle two are signal/power layers. The power traces on the signal layer use wide routing, which lowers the path impedance for power currents and also reduces the impedance of the signal microstrip path. From an EMI control perspective, this is the best existing structure for 4-layer PCBs. The second option has power and ground on the outer layers, with signals routed on the middle two layers. This option improves performance over traditional 4-layer boards but is less effective, as the inter-layer impedance remains similarly poor.

To control trace impedance, both stacking schemes require a careful route of traces underneath the copper islands of power and ground. Additionally, the copper islands on the power or ground layers should be interconnected as much as possible to ensure DC and low-frequency connectivity.

Power Bus

Properly placing appropriately sized capacitors near the power pins of ICs can help achieve faster transitions in IC output voltage. However, the problem doesn’t end there. Due to the limited frequency response of capacitors, they cannot provide the clean harmonic power required to drive IC outputs across the entire frequency range. Moreover, transient voltages formed on the power bus will cause voltage drops across the inductance of the decoupling path, which are the main sources of common-mode EMI interference. How can we address these issues?

For the ICs on our circuit board, the power layer surrounding the IC can be viewed as an excellent high-frequency capacitor, collecting energy leaked from discrete capacitors that provide clean output at high frequencies. Additionally, a good power layer has low inductance, resulting in smaller transient signals, which in turn reduces common-mode EMI.

Of course, the connections from the power layer to the IC power pins must be as short as possible. As the rise times of digital signals become faster, it is best to connect directly to the pads of the IC power pins, which requires further discussion.